ąÆ čĆčāą▒čĆąĖą║čā "ąĀąĄčłąĄąĮąĖčÅ ąŠą┐ąĄčĆą░č鹊čĆčüą║ąŠą│ąŠ ą║ą╗ą░čüčüą░" | ąÜ čüą┐ąĖčüą║čā čĆčāą▒čĆąĖą║ | ąÜ čüą┐ąĖčüą║čā ą░ą▓č鹊čĆąŠą▓ | ąÜ čüą┐ąĖčüą║čā ą┐čāą▒ą╗ąĖą║ą░čåąĖą╣

ąśąĮč鹥čĆč乥ą╣čüčŗ ąĖ ą┐ąŠą┤čāčĆąŠą▓ąĮąĖ PHY ąĖ MAC

ąŻąĮąĖą║ą░ą╗čīąĮą░čÅ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéčī čāčĆąŠą▓ąĮčÅ 40/100GE PHY (ą┐ąŠ čüčĆą░ą▓ąĮąĄąĮąĖčÄ čü 10GE PHY) čüąŠčüč鹊ąĖčé ą▓ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĖ ą╝ąĮąŠą│ąŠą┐ąŠč鹊ą║ąŠą▓ąŠą╣ ą╝ą░čüčłčéą░ą▒ąĖčĆčāąĄą╝ąŠą╣ čüčģąĄą╝čŗ, ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĄą╣ ą┤ąŠčüčéąĖčćčī ą▓čŗčüąŠą║ąĖčģ čüą║ąŠčĆąŠčüč鹥ą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ. ą×ąĮą░ čüąĮąĖąČą░ąĄčé čüą║ąŠčĆąŠčüčéčī ą║ą░ąČą┤ąŠą│ąŠ ą┐ąŠč鹊ą║ą░ ą┤ąŠ 10/25 ąōą▒ąĖčé/čü. ą¤čĆąĖ čŹč鹊ą╝ ą┤ą╗čÅ čāčĆąŠą▓ąĮčÅ PHY ąĮąĄ ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąŠą┤čāčĆąŠą▓ąĄąĮčī WA N PHY, ą▓ą▓ąĄą┤ąĄąĮąĮčŗą╣ ą▓ 10GE ą┤ą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ c č鹥čģąĮąŠą╗ąŠą│ąĖąĄą╣ SDH, čéą░ą║ ą║ą░ą║ ą▓ ąĖč鹊ą│ąŠą▓ąŠą╝ čüčéą░ąĮą┤ą░čĆč鹥 [8] WAN-ąĖąĮč鹥čĆč乥ą╣čüčŗ čĆąĄą░ą╗ąĖąĘčāčÄčéčüčÅ ąĮą░ ąŠčüąĮąŠą▓ąĄ čĆąĄą║ąŠą╝ą╝ąĄąĮą┤ą░čåąĖąĖ G.709 (OTN), ą░ ąĮąĄ G.707 (SDH).

ąŁč鹊čé čüčéą░ąĮą┤ą░čĆčé [8] ą▓ą║ą╗čÄčćą░ąĄčé ą▓čüąĄ ąĖąĘą╝ąĄąĮąĄąĮąĖčÅ, ą▓ąĮąĄčüąĄąĮąĮčŗąĄ ą▓ IEEE 802.3-2008, ą░ čéą░ą║ąČąĄ ąĮąŠą▓čŗąĄ čĆą░ąĘą┤ąĄą╗čŗ ąĖ ą┐čĆąĖą╗ąŠąČąĄąĮąĖčÅ. ąŁčéąĖ ą╝ą░č鹥čĆąĖą░ą╗čŗ č乊čĆą╝ąĖčĆčāčÄčé ąöąŠą┐ąŠą╗ąĮąĄąĮąĖąĄ (Amendment) 4, čüąŠą┤ąĄčƹȹ░čēąĄąĄ ąĮąŠą▓čŗąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ ą┐ąŠą┤čāčĆąŠą▓ąĮčÅ MAC ąĖ čāčĆąŠą▓ąĮčÅ PHY, ą░ čéą░ą║ąČąĄ ą┐ą░čĆą░ą╝ąĄčéčĆčŗ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ ą┤ą╗čÅ ą┐ąĄčĆąĄą┤ą░čćąĖ ą║ą░ą┤čĆąŠą▓ ąĮą░ čüą║ąŠčĆąŠčüčéčÅčģ 40/100 ąōą▒ąĖčé/čü.

ąÆąŠ-ą┐ąĄčĆą▓čŗčģ, ąĮąŠą▓ą░čÅ ą▓ąĄčĆčüąĖčÅ ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ą┤ą╗čÅ čüąŠą▓ą╝ąĄčüčéąĖą╝ąŠčüčéąĖ 6 ąĮąŠą▓čŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓:

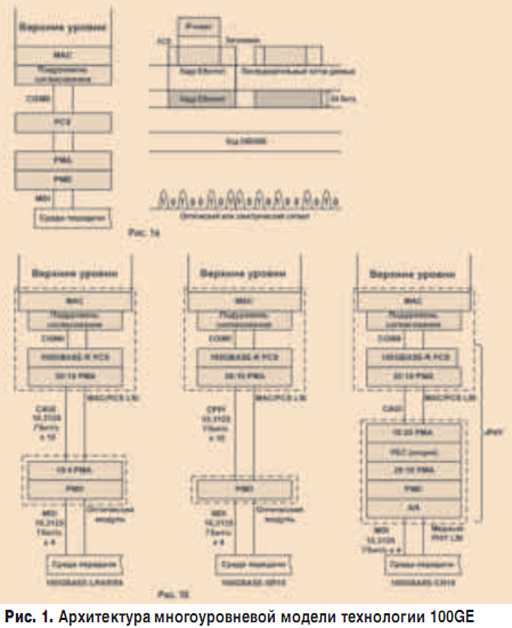

MAC-ą┐ąŠą┤čāčĆąŠą▓ąĄąĮčī ąĖ ąĄą│ąŠ čĆąŠą╗čī čü čĆąŠčüč鹊ą╝ čüą║ąŠčĆąŠčüčéąĖ ą┐ąŠč鹊ą║ą░ ąĮąĄ ąĖąĘą╝ąĄąĮąĖą╗ąĖčüčī [9]. ą×ąĮ, ą║ą░ą║ ąĖ čĆą░ąĮčīčłąĄ, ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé ą┐ą░ą║ąĄčéčŗ ą▓ąĄčĆčģąĮąĄą│ąŠ čāčĆąŠą▓ąĮčÅ ą▓ ą║ą░ą┤čĆčŗ Ethernet, ą░ ąĖą╝ąĄąĮąĮąŠ: čüąĄą│ą╝ąĄąĮčéąĖčĆčāąĄčé ą┐ą░ą║ąĄčéčŗ ą┤ą╗čÅ ąĖąĮą║ą░ą┐čüčāą╗čÅčåąĖąĖ ą▓ ą║ą░ą┤čĆ Ethernet, ą┤ąŠą▒ą░ą▓ą╗čÅąĄčé ą║ ąĘą░ą│ąŠą╗ąŠą▓ą║čā ą┐čĆąĄą░ą╝ą▒čāą╗čā ąĖ MAC-ą░ą┤čĆąĄčü, ą░ čéą░ą║ąČąĄ č乊čĆą╝ąĖčĆčāąĄčé ą║ąŠąĮčéčĆąŠą╗čīąĮčāčÄ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮąŠčüčéčī (FCS) (čüą╝. čĆąĖčü. 1 ą░).

ą¤ąŠą┤čāčĆąŠą▓ąĄąĮčī čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĖčÅ (RS) č乊čĆą╝ąĖčĆčāąĄčé ąĖąĮč鹥čĆč乥ą╣čü ą╝ąĄąČą┤čā RS ąĖ ą┐ąŠą┤čāčĆąŠą▓ąĮąĄą╝ ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ PCS, ą║ą░ą║ ą╗ąŠą│ąĖč湥čüą║ąĖą╣ 100-ą│ąĖą│ą░ą▒ąĖčéąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü CGMII, č鹊 ąĄčüčéčī ą┐čĆąĄąŠą▒čĆą░ąĘčāąĄčé (čü ą┐ąŠą╝ąŠčēčīčÄ PCS) ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗąĄ ą┐ąŠč鹊ą║ąĖ MAC-ą┐ąŠą┤čāčĆąŠą▓ąĮčÅ ą▓ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗąĄ 64-ą▒ąĖčéąĮčŗąĄ ą┐ąŠč鹊ą║ąĖ ą┤ą░ąĮąĮčŗčģ (čü ąĖąĮč鹥čĆč乥ą╣čüąĮčŗą╝ ą║ąŠą┤ąŠą╝ 64B/66B) (čüą╝. čĆąĖčü. 1 ą░).

CGMII ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą║ą░ą║ ąĖąĮč鹥čĆč乥ą╣čü ą╝ąĄąČą┤čā 100GE MAC ąĖ čāčĆąŠą▓ąĮąĄą╝ PHY. ąØąĖąČąĄ ąŠąĮ čĆą░ąĘą▒ąĖą▓ą░ąĄčéčüčÅ ąĮą░ 3ŌĆō5 ą┐ąŠą┤čāčĆąŠą▓ąĮąĄą╣: PCS, PMA, PMD, FEC ąĖ AN (ą┐ąŠčüą╗ąĄą┤ąĮąĖčģ ą┤ą▓čāčģ ąĮąĄčé ą▓ 10GE) čü ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ ą╝ąĄąČą┤čā ąĮąĖą╝ąĖ: CAUI, CPPI (ąĖčģ ąĮąĄčé ą▓ 10GE) ąĖ MDI (čĆąĖčü. 1 ą░, ą▒).

ą¤ąŠą╝ąĄčģąŠčāčüč鹊ą╣čćąĖą▓ąŠąĄ ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ FEC (ąŠą┐čåąĖąŠąĮą░ą╗čīąĮąŠ). ąĢą│ąŠ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéčī ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą┐ąŠą┤čāčĆąŠą▓ąĮąĄą╝ AN. ą×ąĮ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ ą┤ą╗čÅ čāą╗čāčćčłąĄąĮąĖčÅ čāčĆąŠą▓ąĮčÅ BER (ą▓ąĄčĆčüąĖąĖ 100GBASE-CR10 ąĖ 40GBASE-CR4/KR4).

ąśąĮč鹥čĆč乥ą╣čü CAUI ą┐ąĄčĆąĄą┤ą░ąĄčé ą┐ąŠč鹊ą║ 100 ąōą▒ąĖčé/čü č湥čĆąĄąĘ ą┤ąĄčüčÅčéčī 10-ą│ąĖą│ą░ą▒ąĖčéąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ ą┐čĆąĖ ąŠą┐čéąĖč湥čüą║ąŠą╣ ą┐ąĄčĆąĄą┤ą░č湥 ąĮą░ ą║ąŠčĆąŠčéą║ąĖąĄ ą┤ąĖčüčéą░ąĮčåąĖąĖ (100GBASE-CR10) ąĖą╗ąĖ č湥čĆąĄąĘ č湥čéčŗčĆąĄ 25-ą│ąĖą│ą░ą▒ąĖčéąĮčŗčģ ą┐ąŠčüą╗ąĄą┤ąŠą▓ą░č鹥ą╗čīąĮčŗčģ ąĖąĮč鹥čĆč乥ą╣čüą░ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ąĮą░ ą┤ą╗ąĖąĮąĮčŗąĄ ą┤ąĖčüčéą░ąĮčåąĖąĖ (100GBASE-LR4). ąśąĮč鹥čĆč乥ą╣čü CPPI ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ, ą║ą░ą║ ąĖ CAUI, ą┤ą╗čÅ 10-ą┐ąŠč鹊ą║ąŠą▓ąŠą╣ ą┐ąĄčĆąĄą┤ą░čćąĖ ąŠą▒čēąĄą│ąŠ 100-ą│ąĖą│ą░ą▒ąĖčéąĮąŠą│ąŠ ą┐ąŠč鹊ą║ą░ ąĮą░ ą║ąŠčĆąŠčéą║ąĖąĄ ą┤ąĖčüčéą░ąĮčåąĖąĖ (100GBASE-SR10).

ąÆ ą╗ąŠą│ąĖč湥čüą║ąĖčģ ą▒ą╗ąŠą║ą░čģ MAC/PCS LSI (čĆąĖčü. 1 ą▒) ąĮą░ ą┐ąŠą┤čāčĆąŠą▓ąĮąĄ PCS 66-ą▒ąĖčéąĮčŗąĄ ą▒ą╗ąŠą║ąĖ ą┤ą░ąĮąĮčŗčģ čü ą║ąŠą┤ąŠą╝ 64B/66B čĆą░čüą┐čĆąĄą┤ąĄą╗čÅčÄčéčüčÅ čåąĖą║ą╗ąĖč湥čüą║ąĖ ą┐ąŠ 20 ą╗ąŠą│ąĖč湥čüą║ąĖą╝ ą┐ąŠč鹊ą║ą░ą╝. ąŻčćąĖčéčŗą▓ą░čÅ, čćč鹊 ą┐ąŠčüą╗ąĄ 64B/66B-ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ čüą║ąŠčĆąŠčüčéčī 100G-čüąĖą│ąĮą░ą╗ą░ čüčéą░ąĮąŠą▓ąĖčéčüčÅ 103,125 ąōą▒ąĖčé/čü, ą┐ąŠą╗čāčćą░ąĄą╝, čćč鹊 čüą║ąŠčĆąŠčüčéčī ąŠą┤ąĮąŠą│ąŠ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ ą┐ąŠč鹊ą║ą░ ŌĆō 5,15625 ąōą▒ąĖčé/čü. ąÆ ą┐ąŠą┤čāčĆąŠą▓ąĮąĄ PMA čāą║ą░ąĘą░ąĮąĮčŗąĄ 20 ą┐ąŠč鹊ą║ąŠą▓ ą╝ąŠąČąĮąŠ ą║ąŠąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░čéčī (ą┐čāč鹥ą╝ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖčÅ čü ą▒ąĖčé-ąĖąĮč鹥čĆą╗ąĖą▓ąĖąĮą│ąŠą╝ [3]) ą▓ čéčĆąĄą▒čāąĄą╝ąŠąĄ čćąĖčüą╗ąŠ čäąĖąĘąĖč湥čüą║ąĖčģ ą┐ąŠč鹊ą║ąŠą▓ (ą║čĆą░čéąĮąŠčüčéčī ą▓čŗčģąŠą┤ą░ 1, 2, 4, 5 ąĖ 10). ąĪčéą░ąĮą┤ą░čĆčé ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé č鹊ą╗čīą║ąŠ ą║čĆą░čéąĮąŠčüčéąĖ 4 ąĖ 10. ąÆ ą┐ąĄčĆą▓ąŠą╝ čüą╗čāčćą░ąĄ čüą║ąŠčĆąŠčüčéčī čäąĖąĘąĖč湥čüą║ąŠą│ąŠ ą┐ąŠč鹊ą║ą░ čüąŠčüčéą░ą▓ąĖčé 25,78125 (100/4), ą░ ą▓ąŠ ą▓č鹊čĆąŠą╝ ŌĆō 10,3125 ąōą▒ąĖčé/čü (100/10).

ąóą░ą║ ą║ą░ą║ čćąĖčüą╗ąŠ ąĖčüčģąŠą┤ąĮčŗčģ ą╗ąŠą│ąĖč湥čüą║ąĖčģ ą┐ąŠč鹊ą║ąŠą▓ ą▓ąĄą╗ąĖą║ąŠ (20), ą╝ąŠą│čāčé ą▓ąŠąĘąĮąĖą║ąĮčāčéčī ą┐ąĄčĆąĄą║ąŠčüčŗ ąĖąĘ-ąĘą░ ą┤ąČąĖčéč鹥čĆą░ ąĖ čĆą░ąĘą╗ąĖčćąĖčÅ ą▓čĆąĄą╝ąĄąĮąĖ ą┐čĆąĖčģąŠą┤ą░. ą×ąĮąĖ ą║ąŠą╝ą┐ąĄąĮčüąĖčĆčāčÄčéčüčÅ ą▓čüčéą░ą▓ą║ąŠą╣ (č湥čĆąĄąĘ ą║ą░ąČą┤čŗąĄ 16 383 ą║ąŠą┤ąŠą▓čŗčģ 66-ą▒ąĖč鹊ą▓čŗčģ ą▒ą╗ąŠą║ą░) čüą┐ąĄčåąĖą░ą╗čīąĮčŗčģ ą▓čŗčĆą░ą▓ąĮąĖą▓ą░čÄčēąĖčģ 66-ą▒ąĖč鹊ą▓čŗčģ ą╝ą░čĆą║ąĄčĆąŠą▓, čüąŠą┤ąĄčƹȹ░čēąĖčģ ąĮąŠą╝ąĄčĆ ą╗ąŠą│ąĖč湥čüą║ąŠą│ąŠ ą┐ąŠč鹊ą║ą░ ąĖ ą┐ąŠą╗ąĄ ą┐čĆąŠą▓ąĄčĆą║ąĖ ąĮą░ č湥čéąĮąŠčüčéčī č湥čĆąĄą┤čāčÄčēąĖčģčüčÅ ą▒ąĖčé čéąĖą┐ą░ BIP.

ą¤ąŠą┤čāčĆąŠą▓ąĄąĮčī PMA ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé ą║ąŠąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░ąĮąĖąĄ 20:10 ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ 10-ą│ąĖą│ą░ą▒ąĖčéąĮčŗčģ ą┐ąŠč鹊ą║ąŠą▓ ąĖ 10:4 ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ 25-ą│ąĖą│ą░ą▒ąĖčéąĮčŗčģ ą┐ąŠč鹊ą║ąŠą▓.

ą¤ąŠą┤čāčĆąŠą▓ąĄąĮčī FEC ą▓ą║ą╗čÄčćą░ąĄčéčüčÅ ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓ą░čĆąĖą░ąĮč鹊ą▓ 40/100GBASE-R FEC, ąĖčüą┐ąŠą╗čīąĘčāąĄą╝čŗčģ ą┐čĆąĖ ą┐ąĄčĆąĄą┤ą░č湥 ą┐ąŠ ą╝ąĄą┤ąĮąŠą╣ ą┐ą░čĆąĄ (ąĖą╗ąĖ ą┐čĆąĖ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĖ ąĮą░ ąĘą░ą┤ąĮąĄą╣ ą┐ą░ąĮąĄą╗ąĖ ą║ąŠą╝ą┐čīčÄč鹥čĆąŠą▓) ąĖ ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĖčģ ąĮą░ 2 ą┤ąæ čāą╗čāčćčłąĖčéčī BER ąĖ ąĖčüą┐čĆą░ą▓ą╗čÅčéčī ą┐ą░čćą║ąĖ ąŠčłąĖą▒ąŠą║. ąöą╗čÅ čŹč鹊ą╣ čåąĄą╗ąĖ ą┐čĆąĖą╝ąĄąĮčÅąĄčéčüčÅ čāą║ąŠčĆąŠč湥ąĮąĮčŗą╣ čåąĖą║ą╗ąĖč湥čüą║ąĖą╣ ą║ąŠą┤ ążą░ą╣ąĄčĆą░ (Fire code ŌĆō FC) čü 32-ą▒ąĖčéąĮąŠą╣ č湥čéąĮąŠčüčéčīčÄ (ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąŠč鹊ą║ą░), ą┐ąŠąĘą▓ąŠą╗čÅčÄčēąĖą╣ ąĖčüą┐čĆą░ą▓ą╗čÅčéčī ą┐ą░čćą║ąĖ ąŠčłąĖą▒ąŠą║ ą┤ą╗ąĖąĮąŠą╣ ą┤ąŠ 11 ą▒ąĖčé [9, 10].

ąÆ čĆąĄąĘčāą╗čīčéą░č鹥 ą┤ą╗čÅ 40/100GE ą┐ąŠą╗čāčćą░ąĄą╝ čüą╗ąĄą┤čāčÄčēčāčÄ ą║ą░čĆčéąĖąĮčā ą┐ąŠą┤čāčĆąŠą▓ąĮąĄą╣ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ.

ąśąĮč鹥čĆč乥ą╣čü MII (Media Independent Interface), ąĮąĄąĘą░ą▓ąĖčüąĖą╝čŗą╣ ąŠčé čüčĆąĄą┤čŗ ą┐ąĄčĆąĄą┤ą░čćąĖ, ŌĆō ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ą╗ąŠą│ąĖč湥čüą║ąŠąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā MAC-ą┐ąŠą┤čāčĆąŠą▓ąĮąĄą╝ ąĖ čüąŠčüčéą░ą▓ą╗čÅčÄčēąĖą╝ąĖ čāčĆąŠą▓ąĮčÅ PHY. ą×ąĮ ąĮąĄ čéčĆąĄą▒čāąĄčé čäąĖąĘąĖč湥čüą║ąŠą╣ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ąĖ čüąŠąĄą┤ąĖąĮčÅąĄčé čāčĆąŠą▓ąĮąĖ ą▓ąĮčāčéčĆąĖ ą║ą░ą║ąŠą│ąŠ-č鹊 čāčüčéčĆąŠą╣čüčéą▓ą░ ą╗ąŠą│ąĖč湥čüą║ąĖ.

ąśąĮč鹥čĆč乥ą╣čü XLGMII ŌĆō ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░ąĄčé 40-ą│ąĖą│ą░ą▒ąĖčéąĮčŗąĄ, ą░ ąĖąĮč鹥čĆč乥ą╣čü CGMII ŌĆō 100-ą│ąĖą│ą░ą▒ąĖčéąĮčŗąĄ ąŠą┐ąĄčĆą░čåąĖąĖ ą▓ ą┐čĆąŠčåąĄčüčüąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░ ą┐čĆąŠčģąŠą┤čÅčēąĖčģ č湥čĆąĄąĘ ąĮąĖčģ 64-ą▒ąĖčéąĮčŗčģ ą┐ąŠč鹊ą║ąŠą▓ ą┤ą░ąĮąĮčŗčģ, č鹊ą│ą┤ą░ ą║ą░ą║ ą┐ąŠą┤čāčĆąŠą▓ąĄąĮčī RS ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ąŠč鹊ą▒čĆą░ąČąĄąĮąĖąĄ ą╝ąĄąČą┤čā čüąĖą│ąĮą░ą╗ą░ą╝ąĖ, č乊čĆą╝ąĖčĆčāąĄą╝čŗą╝ąĖ ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ XLGMII ąĖ CGMII ąĖ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖčÅą╝ąĖ čüąĄčĆą▓ąĖčüą░ MAC/PLS. ąØąĄčüą╝ąŠčéčĆčÅ ąĮą░ č鹊 čćč鹊 ąĖąĮč鹥čĆč乥ą╣čüčŗ XLGMII ąĖ CGMII ąŠą┐čåąĖąŠąĮą░ą╗čīąĮčŗ, ąŠąĮąĖ čłąĖčĆąŠą║ąŠ ą┐čĆąĖą╝ąĄąĮčÅčÄčéčüčÅ ą▓ čüčéą░ąĮą┤ą░čĆč鹥 ą║ą░ą║ ąŠčüąĮąŠą▓ą░ ą┤ą╗čÅ čäčāąĮą║čåąĖąŠąĮą░ą╗čīąĮąŠą╣ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ, ąĖ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčé ąŠą▒čēąĖą╣ čüąĄčĆą▓ąĖčüąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü ą┤ą╗čÅ ą┐ąŠą┤čāčĆąŠą▓ąĮąĄą╣ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ, ąŠą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ą▓ čüčéą░ąĮą┤ą░čĆč鹥 [8].

ąóąĄčĆą╝ąĖąĮčŗ 40/100GBASE-R ąŠčéąĮąŠčüčÅčéčüčÅ ą║ ąŠčüąŠą▒ąŠą╣ ą│čĆčāą┐ą┐ąĄ čĆąĄą░ą╗ąĖąĘą░čåąĖą╣ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ, ąŠčüąĮąŠą▓ą░ąĮąĮąŠą╣ ąĮą░ ą╝ąĄč鹊ą┤ąĄ ą▒ą╗ąŠčćąĮąŠą│ąŠ ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ ą║ąŠą┤ąŠą╝ 64B/66B ąĖ čüą┐ąĄčåąĖčäąĖą║ą░čåąĖąĖ PMA. 40/100GBASE-R PCS ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčé: ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ/ą┤ąĄą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ, ą┐ąŠą╗čāč湥ąĮąĮčŗčģ ąŠčé ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ (ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░ąĮąĮčŗčģ ąĮą░ ąĖąĮč鹥čĆč乥ą╣čüčŗ) XLGMII/CGMII ą▓ ą▓ąĖą┤ąĄ ą▒ą╗ąŠą║ąŠą▓ ą║ąŠą┤ą░ 64B/66B; čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĖąĄ ą┤ą░ąĮąĮčŗčģ ą┐ąŠ ąĮąĄčüą║ąŠą╗čīą║ąĖą╝ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╝ ą┐ąŠč鹊ą║ą░ą╝ (lanes) ąĖ ą┐ąĄčĆąĄą┤ą░čćčā ą┤ą░ąĮąĮčŗčģ ąĮą░ PMA.

ą¤ąŠą┤čāčĆąŠą▓ąĄąĮčī FEC ŌĆō ąŠą┐čåąĖąŠąĮą░ą╗ąĄąĮ ą┤ą╗čÅ 40/100GBASE-R, čĆą░čüčüčćąĖčéą░ąĮąĮčŗčģ ąĮą░ ą┐ąĄčĆąĄą┤ą░čćčā ą┐ąŠ ą╝ąĄą┤ąĮąŠą╣ ą┐ą░čĆąĄ (STP) ąĖą╗ąĖ ą┐ąĄčĆąĄą┤ą░čćčā ąĮą░ ąĘą░ą┤ąĮąĄą╣ ą┐ą░ąĮąĄą╗ąĖ PHY. ą×ąĮ ą╝ąŠąČąĄčé ą▒čŗčéčī ą┐ąŠą╝ąĄčēąĄąĮ ą╝ąĄąČą┤čā ą┐ąŠą┤čāčĆąŠą▓ąĮčÅą╝ąĖ PCS ąĖ PMA ąĖą╗ąĖ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ą┐ąŠą┤čāčĆąŠą▓ąĮčÅą╝ąĖ PMA, čĆąĄą░ą╗ąĖąĘčāąĄčéčüčÅ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąŠč鹊ą║ą░ PCS (PCS-lane) ąŠčéą┤ąĄą╗čīąĮąŠ ąĖ čĆą░ą▒ąŠčéą░ąĄčé ą░ą▓č鹊ąĮąŠą╝ąĮąŠ ą┤ą╗čÅ ą║ą░ąČą┤ąŠą│ąŠ ą┐ąŠč鹊ą║ą░ PCS.

AN ŌĆō ą┐ąŠą┤čāčĆąŠą▓ąĄąĮčī čüąŠą│ą╗ą░čüąŠą▓ą░ąĮąĖčÅ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠčüčéąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĖąĄ FEC, ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░čÄčēąĖą╣ ąĮą░ą╗ąĖčćąĖąĄ čéą░ą║ąŠą│ąŠ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą│ąŠ čāčüčéčĆąŠą╣čüčéą▓ą░, ą║ąŠč鹊čĆąŠąĄ ą╝ąŠąČąĄčé ąŠą▒ąĮą░čĆčāąČąĖčéčī ąĮą░ ą┤čĆčāą│ąŠą╝ ą║ąŠąĮčåąĄ ąĘą▓ąĄąĮą░ čüą▓čÅąĘąĖ čāčüčéčĆąŠą╣čüčéą▓ąŠ, ąŠą▒ą╗ą░ą┤ą░čÄčēąĄąĄ čéą░ą║ąĖą╝ ąČąĄ čĆąĄąČąĖą╝ąŠą╝ čĆą░ą▒ąŠčéčŗ, ąĖ, ąŠą┐čĆąĄą┤ąĄą╗ąĖą▓ ąĮą░ą╗ąĖčćąĖąĄ ąŠą▒čēąĖčģ ą▓ąŠąĘą╝ąŠąČąĮąŠčüč鹥ą╣, čüą║ąŠąĮčäąĖą│čāčĆąĖčĆąŠą▓ą░čéčī čĆąĄą░ą╗ąĖąĘą░čåąĖčÄ čüąŠą▓ą╝ąĄčüčéąĮąŠą╣ ąŠą┐ąĄčĆą░čåąĖąĖ. AN ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ 40-ą│ąĖą│ą░ą▒ąĖčéąĮąŠą╣ ąĘą░ą┤ąĮąĄą╣ ą┐ą░ąĮąĄą╗čīčÄ čāčĆąŠą▓ąĮčÅ PHY ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ Ethernet čéąĖą┐ą░ 40GBASE-KR4 ąĖ ą┐ąŠč鹊ą║ąŠą▓ 40/100 ąōą▒ąĖčé/čü ą┐ąŠ STP čäąĖąĘąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ą┤ą╗čÅ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ Ethernet čéąĖą┐ą░ 40GBASE-CR4 ąĖ 100GBASE-CR10.

ą¤ąŠą┤čāčĆąŠą▓ąĄąĮčī PMA ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ą┤ą╗čÅ PCS ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠąĄ ąŠčé čüčĆąĄą┤čŗ ą┐ąĄčĆąĄą┤ą░čćąĖ čüčĆąĄą┤čüčéą▓ąŠ ą┐ąŠą┤ą┤ąĄčƹȹ║ąĖ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čĆą░ąĘą╗ąĖčćąĮčŗčģ čäąĖąĘąĖč湥čüą║ąĖčģ čüčĆąĄą┤ ą┐ąĄčĆąĄą┤ą░čćąĖ. ąöąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮąŠ ąŠąĮ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčé (ą┐ąŠ čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÄ) čĆąĄčéą░ą╣ą╝ąĖąĮą│ (ą▓ąŠčüčüčéą░ąĮąŠą▓ą╗ąĄąĮąĖąĄ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ) ą┐čĆąĖąĮčÅčéčŗčģ ą┤ą░ąĮąĮčŗčģ ąĖ ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé ąĖčģ č鹥čüčéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĖ ąŠą▒čēąĖą╣ ą║ąŠąĮčéčĆąŠą╗čī.

ą¤ąŠą┤čāčĆąŠą▓ąĄąĮčī PMD ąŠčéą▓ąĄčćą░ąĄčé ąĘą░ ąĖąĮč鹥čĆč乥ą╣čü ą┤ą░ąĮąĮčŗčģ, ą┐ąĄčĆąĄą┤ą░ą▓ą░ąĄą╝čŗčģ ą▓ čüčĆąĄą┤čā ą┐ąĄčĆąĄą┤ą░čćąĖ, ąĖ čĆą░čüą┐ąŠą╗ą░ą│ą░ąĄčéčüčÅ ąĮąĄą┐ąŠčüčĆąĄą┤čüčéą▓ąĄąĮąĮąŠ ąĮą░ą┤ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ MDI, ą║ąŠč鹊čĆčŗą╣ ąŠčéąĮąŠčüąĖčéčüčÅ ą║ ą║ą░č鹥ą│ąŠčĆąĖąĖ 菹╗ąĄą╝ąĄąĮč鹊ą▓, ą▓ą║ą╗čÄčćą░ąĄą╝čŗčģ ą▓ ą║ą░ąČą┤čŗą╣ ą┐ąŠą┤čāčĆąŠą▓ąĄąĮčī PMD, ąĖ čäą░ą║čéąĖč湥čüą║ąĖ čÅą▓ą╗čÅąĄčéčüčÅ ą┐ąŠą┤čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄą╝ ą║ čüčĆąĄą┤ąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ.

ą”ąĄą╗čī ąĖąĮč鹥čĆč乥ą╣čüąŠą▓ XLAUI/CAUI ŌĆō ąŠą▒ąĄčüą┐ąĄčćąĖčéčī ą│ąĖą▒ą║ąŠąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā ą┤ą▓čāą╝čÅ ąśąĪ ąĖą╗ąĖ ą╝ąĄąČą┤čā ąśąĪ ąĖ ą╝ąŠą┤čāą╗ąĄą╝ ą┤ą╗čÅ 40/100-ą│ąĖą│ą░ą▒ąĖčéąĮčŗčģ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ą┐čĆąĖ ą┤ą╗ąĖąĮąĄ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ ąĮą░ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░č鹥 ą┤ąŠ 25 čüą╝, ą▓ą║ą╗čÄčćą░čÅ čĆą░ąĘčŖąĄą╝. ąśąĮč鹥čĆč乥ą╣čü CAUI ą╝ąŠąČąĄčé ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā 10-ą┐ąŠč鹊čćąĮčŗą╝ ą┐ąŠą┤čāčĆąŠą▓ąĮąĄą╝ PMA (čüą║ąŠčĆąŠčüčéčī ą┐ąĄčĆąĄą┤ą░čćąĖ 100 ąōą▒ąĖčé/čü) ąĖ 菹╗ąĄą╝ąĄąĮč鹊ą╝ ąŠč鹊ą▒čĆą░ąČąĄąĮąĖčÅ 10:4 PMA. ąÉ ąĖąĮč鹥čĆč乥ą╣čü XLAUI ą╝ąŠąČąĄčé ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čāą┤ą╗ąĖąĮąĄąĮąĖąĄ ą┐ąŠč鹊ą║ą░ ą┤ą╗čÅ čüąŠąĄą┤ąĖąĮąĄąĮąĖčÅ čĆą░čüą┐čĆąĄą┤ąĄą╗ąĄąĮąĮčŗčģ ąĮą░ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░č鹥 ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ MAC ąĖ PHY čāčĆąŠą▓ąĮąĄą╣ ą▓ čüąĖčüč鹥ą╝ąĄ 40-ą│ąĖą│ą░ą▒ąĖčéąĮąŠą│ąŠ Ethernet.

ąśąĮč鹥čĆč乥ą╣čü XLAUI/CAUI ąĖą╝ąĄąĄčé čüą╗ąĄą┤čāčÄčēąĖąĄ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ąĖ:

ą¤ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ čäąĖąĘąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü (nPPI) ŌĆō čŹč鹊 čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ čüąĄčĆą▓ąĖčüąĮąŠą│ąŠ ąĖąĮč鹥čĆč乥ą╣čüą░ PMD. ą×ąĮ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą║ąŠąĮčüčéčĆčāąĖčĆąŠą▓ą░čéčī ą║ąŠą╝ą┐ą░ą║čéąĮčŗąĄ ą╝ąŠą┤čāą╗ąĖ ąŠą┐čéąĖč湥čüą║ąĖčģ čéčĆą░ąĮčüąĖą▓ąĄčĆąŠą▓ ą┤ą╗čÅ 40GBASE-SR4/LR4 ąĖą╗ąĖ 100GBASE-SR10. 40-ą│ąĖą│ą░ą▒ąĖčéąĮčŗą╣ PPI (XLPPI, 4 ą┐ąŠč鹊ą║ą░) ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ čü 40GBASE-SR4/LR4, ą░ 100-ą│ąĖą│ą░ą▒ąĖčéąĮčŗą╣ PPI (CPPI, 10 ą┐ąŠč鹊ą║ąŠą▓) ŌĆō čü 100GBASE-SR10.

ą¤ąŠą┤čāčĆąŠą▓ąĮąĖ PMD ąĖ PMA ąĮčāąČąĮąŠ ą┐ąŠą┤ą║ą╗čÄčćą░čéčī ą║ ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ nPPI, čćč鹊ą▒čŗ čāą┤ąŠą▓ą╗ąĄčéą▓ąŠčĆąĖčéčī čéčĆąĄą▒ąŠą▓ą░ąĮąĖčÅ ą┐ąŠ ąĘą░ą┤ąĄčƹȹ║ąĄ, ą┐ąĄčĆąĄą║ąŠčüčā ąĖ ą▓ą░čĆąĖą░čåąĖąĖ ą┐ąĄčĆąĄą║ąŠčüą░.

ą×ą┐čåąĖąŠąĮą░ą╗čīąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü MDIO/MDC ŌĆō ąĖąĮč鹥čĆč乥ą╣čü ą▓ą▓ąŠą┤ą░-ą▓čŗą▓ąŠą┤ą░ ą┤ą░ąĮąĮčŗčģ ą╝ąĄąĮąĄą┤ąČą╝ąĄąĮčéą░ (ąĖą╗ąĖ ąĖąĮč鹥čĆč乥ą╣čü čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ) ąŠą▒ąĄčüą┐ąĄčćąĖą▓ą░ąĄčé čüąŠąĄą┤ąĖąĮąĄąĮąĖąĄ ą╝ąĄąČą┤čā čāą┐čĆą░ą▓ą╗čÅąĄą╝čŗą╝ąĖ čāčüčéčĆąŠą╣čüčéą▓ą░ą╝ąĖ MDIO (MMD) ąĖ ą╗ąŠą│ąĖč湥čüą║ąĖą╝ąĖ ąŠą▒čŖąĄą║čéą░ą╝ąĖ čāą┐čĆą░ą▓ą╗ąĄąĮąĖčÅ čĆą░ą▒ąŠčćąĖą╝ąĖ čüčéą░ąĮčåąĖčÅą╝ąĖ (STA).

ąśąĘ 8 ą▓ą░čĆąĖą░ąĮč鹊ą▓ (čéąĖą┐ąŠą▓ ąĖąĮč鹥čĆč乥ą╣čüąŠą▓) Ethernet (čüą╝. čéą░ą▒ą╗. 2) ą╝čŗ čĆą░čüčüą╝ąŠčéčĆąĖą╝ ąŠčüąŠą▒ąĄąĮąĮąŠčüčéąĖ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą┐čÅčéąĖ ą▓ą░čĆąĖą░ąĮč鹊ą▓, čüąŠą▒čĆą░ąĮąĮčŗčģ ą▓ ą┤ą▓ąĄ ą│čĆčāą┐ą┐čŗ: 40/100GBASE-SR4/10 ąĖ 40/100GBASE-LR4+ER4. ą¤ąĄčĆą▓ą░čÅ ą│čĆčāą┐ą┐ą░ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąĄčĆąĄą┤ą░čéčī 4/10 ą┐ąŠč鹊ą║ąŠą▓ ąĮą░ čĆą░čüčüč鹊čÅąĮąĖąĄ 100 ą╝ ą┐ąŠ ą£ą£ ąÆą×ąÜ ą▓ ą┐ąĄčĆą▓ąŠą╝ ąŠą║ąĮąĄ ą┐čĆąŠąĘčĆą░čćąĮąŠčüčéąĖ, č鹊ą│ą┤ą░ ą║ą░ą║ ą▓č鹊čĆą░čÅ ŌĆō ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ą┐ąĄčĆąĄą┤ą░čéčī 4 ą┐ąŠč鹊ą║ą░ ąĮą░ čĆą░čüčüč鹊čÅąĮąĖąĄ 10/40 ą║ą╝ ą┐ąŠ ą×ą£ ąÆą×ąÜ ą▓ąŠ ą▓č鹊čĆąŠą╝ ąŠą║ąĮąĄ ą┐čĆąŠąĘčĆą░čćąĮąŠčüčéąĖ.

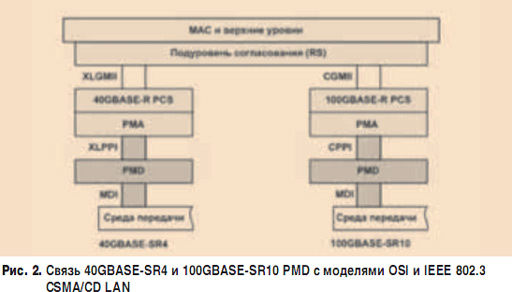

ąĀąĄą░ą╗ąĖąĘčāąĄą╝čŗąĄ ą▓ą░čĆąĖą░ąĮčéčŗ (čüą╝. ą╝ąŠą┤ąĄą╗ąĖ čäąĖąĘąĖč湥čüą║ąŠą│ąŠ čāčĆąŠą▓ąĮčÅ ąĮą░ čĆąĖčü. 2) ą┐ąĄčĆąĄą┤ą░čÄčé ą┐ąŠč鹊ą║ąĖ ą┐ąŠ ą┤ą▓čāą╝ čüčģąĄą╝ą░ą╝:

RS? XLGMII? 40GBASE-R PCS?PMA?XLPPI?PMD?MDI?Me dium;

RS? CGMII? 100GBASE-R PCS? PMA? CPPI? PMD?MDI? Medium.

ą×ą┐čĆąĄą┤ąĄą╗čÅčÄčēąĖą╝ąĖ ąĘą┤ąĄčüčī čÅą▓ą╗čÅčÄčéčüčÅ: ą┐ąŠą┤čāčĆąŠą▓ąĄąĮčī PMD čü ąĖąĮč鹥čĆč乥ą╣čüą░ą╝ąĖ XLPPI/CPPI ąĖ MDI (ą▓čŗą┤ąĄą╗ąĄąĮčŗ ąĮą░ čĆąĖčü. 2), čģąŠčéčÅ ą┤ą╗čÅ č乊čĆą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ą┐ąŠą╗ąĮąŠą│ąŠ PHY-čāčĆąŠą▓ąĮčÅ PMD ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī čüąŠąĄą┤ąĖąĮąĄąĮ čü čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ PMA, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ąĮąŠ ąĮą░ čĆąĖčü. 2, čüąŠ čüčĆąĄą┤ąŠą╣ (č湥čĆąĄąĘ ąĖąĮč鹥čĆč乥ą╣čü MDI). ą¤čĆąĖ čŹč鹊ą╝ 40GBASE-SR4 ąĖčüą┐ąŠą╗čīąĘčāąĄčé 4, ą░ 100GBASE-SR10 ŌĆō 10 ąĖą┤ąĄąĮčéąĖčćąĮčŗčģ ą┐ąŠč鹊ą║ąŠą▓ (lanes), ą┐čĆąŠąĮčāą╝ąĄčĆąŠą▓ą░ąĮąĮčŗčģ ąŠčé 0 ą┤ąŠ n-1, n=4 ąĖą╗ąĖ 10.

ąĪąĄčĆą▓ąĖčüąĮčŗąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ ą┤ą╗čÅ 40GBASE-SR4 ąĖ 100GBASE-SR10 PMD ąŠą┐ąĖčüą░ąĮčŗ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą░ą▒čüčéčĆą░ą║čéąĮąŠ ąĖ ąĮąĄ ą┐ąŠą┤čĆą░ąĘčāą╝ąĄą▓ą░čÄčé ą║ą░ą║ąŠąĄ-č鹊 ą║ąŠąĮą║čĆąĄčéąĮąŠąĄ ąĖčüą┐ąŠą╗ąĮąĄąĮąĖąĄ, čģąŠčéčÅ ą╗ąŠą│ąĖč湥čüą║ąĖ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąŠą▒ą╝ąĄąĮ ą║ąŠą┤ąĖčĆąŠą▓ą░ąĮąĮčŗą╝ąĖ ą┤ą░ąĮąĮčŗą╝ąĖ ą╝ąĄąČą┤čā ąŠą▒čŖąĄą║čéą░ą╝ąĖ PMA ąĖ PMD, čéčĆą░ąĮčüą╗ąĖčĆčāčÅ ą┤ą░ąĮąĮčŗąĄ ą▓ čüąĖą│ąĮą░ą╗čŗ, ą┐ąŠą┤ą░ą▓ą░ąĄą╝čŗąĄ ą▓ čüčĆąĄą┤čā ąĖą╗ąĖ ą┐čĆąĖąĮąĖą╝ą░ąĄą╝čŗąĄ ąĖąĘ ąĮąĄąĄ. ąĪčāą╝ą╝ą░čĆąĮą░čÅ ąĘą░ą┤ąĄčƹȹ║ą░ čüąĖą│ąĮą░ą╗ą░ ą┐čĆąĖ ą┐čĆąŠčģąŠąČą┤ąĄąĮąĖąĖ PMD (čü čāč湥č鹊ą╝ 2 ą╝ ąÆą×ąÜ) ąĮąĄ ą┤ąŠą╗ąČąĮą░ ą┐čĆąĄą▓čŗčłą░čéčī ą┤ą╗čÅ 40GBASE-SR4 1024 ąæąó, ą░ ą┤ą╗čÅ 100GBASE-SR10 ŌĆō 2048 ąæąó.

ąöą╗čÅ Ethernet čéąĖą┐ą░ 40/100GBASE-LR4 ąĖ 100GBASE-ER4 ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą┐čĆąĖą▓ąĄą┤ąĄąĮą░ ąĮą░ čĆąĖčü. 3. ąśąĮč鹥čĆč乥ą╣čü PMD ąĘą┤ąĄčüčī ą▓čŗą┐ąŠą╗ąĮčÅąĄčé čäčāąĮą║čåąĖąĖ ą┐čĆąĖąĄą╝ą░-ą┐ąĄčĆąĄą┤ą░čćąĖ, ą║ąŠč鹊čĆčŗąĄ ą┤ąŠčüčéą░ą▓ą╗čÅčÄčé ą┤ą░ąĮąĮčŗąĄ ą╝ąĄąČą┤čā čüąĄčĆą▓ąĖčüąĮčŗą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ PMD ąĖ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ MDI.

ążčāąĮą║čåąĖčÅ ą┐ąĄčĆąĄą┤ą░čćąĖ PMD ą║ąŠąĮą▓ąĄčĆčéąĖčĆčāąĄčé 4 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖčģ ą▓ 4 ąŠą┐čéąĖč湥čüą║ąĖčģ ą┐ąŠč鹊ą║ą░, ą┤ąŠčüčéą░ą▓ą╗čÅąĄą╝čŗčģ ąĮą░ ąĖąĮč鹥čĆč乥ą╣čü MDI. ążčāąĮą║čåąĖčÅ ą┐čĆąĖąĄą╝ą░ PMD ą║ąŠąĮą▓ąĄčĆčéąĖčĆčāąĄčé 4 ąŠą┐čéąĖč湥čüą║ąĖčģ ą┐ąŠč鹊ą║ą░, ą┐ąŠą╗čāč湥ąĮąĮčŗčģ ąŠčé MDI, ą▓ 4 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖčģ ą┐ąŠč鹊ą║ą░ ą┤ą╗čÅ ą┤ąŠčüčéą░ą▓ą║ąĖ ąĮą░ čüąĄčĆą▓ąĖčüąĮčŗą╣ ąĖąĮč鹥čĆč乥ą╣čü PMD. ą¤čĆąĖč湥ą╝ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗąĄ ą┐ąŠč鹊ą║ąĖ čüąŠą▒ąĖčĆą░čÄčéčüčÅ/čĆą░ąĘą▒ąĖčĆą░čÄčéčüčÅ ąĮą░ čüč鹊čĆąŠąĮąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆąŠą▓/ą┤ąĄą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆąŠą▓ WDM ąĖ ąĖčüą┐ąŠą╗čīąĘčāčÄčé ą×ą£ ą×ąÆ ąÆą×ąÜ ą▓ ą║ą░č湥čüčéą▓ąĄ čüčĆąĄą┤čŗ ą┐ąĄčĆąĄą┤ą░čćąĖ ą┤ą╗čÅ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ ą▒ąŠą╗čīčłąĄą╣ ą┤ą╗ąĖąĮčŗ ą┐ąĄčĆąĄą┤ą░čÄčēąĄą│ąŠ čéčĆą░ą║čéą░ (čüą╝. čéą░ą▒ą╗. 2).

ą¤ąŠą┤čāčĆąŠą▓ąĄąĮčī PMD čüčéą░ąĮą┤ą░čĆčéąĖąĘąŠą▓ą░ąĮ ą▓ č鹥čüč鹊ą▓čŗčģ č鹊čćą║ą░čģ (TPn). ąŁą╗ąĄą║čéčĆąĖč湥čüą║ąĖą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ą┐ąĄčĆąĄą┤ą░čÄčēąĄą╣ čüč鹊čĆąŠąĮąĄ (PMA-PMD) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▓ č鹊čćą║ąĄ TP1; ąŠą┐čéąĖč湥čüą║ąĖą╣ ŌĆō ą▓ č鹊čćą║ąĄ TP2 (ąĮą░ ą▓čŗčģąŠą┤ąĄ 2ŌĆō5 ą╝ ą×ąÆ-ą┐ą░čéčć-ą║ąŠčĆą┤ą░); ąŠą┐čéąĖč湥čüą║ąĖą╣ čüąĖą│ąĮą░ą╗ ą┐čĆąĖąĄą╝ą░ ŌĆō ą▓ č鹊čćą║ąĄ TP3 (ąĮą░ ą▓čŗčģąŠą┤ąĄ ą£ą£ ąÆą×ąÜ čā ąĖąĮč鹥čĆč乥ą╣čüą░ MDI); 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖą╣ čüąĖą│ąĮą░ą╗ ąĮą░ ą┐čĆąĖąĄą╝ąĮąŠą╣ čüč鹊čĆąŠąĮąĄ (PMD-PMA) ąŠą┐čĆąĄą┤ąĄą╗čÅąĄčéčüčÅ ą▓ č鹊čćą║ąĄ TP4.

ąÉąĮą░ą╗ąŠą│ąĖčćąĮąŠ ą┐čĆąĄą┤čŗą┤čāčēąĄą╣ ą▒čāą┤ąĄčé ą▓čŗą│ą╗čÅą┤ąĄčéčī ąĖ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ ą┤ą╗čÅ ą┤ą▓čāčģ ą┤čĆčāą│ąĖčģ čéąĖą┐ąŠą▓ Ethernet: 40GBASE-SR4 ąĖ 100GBASE-SR10. ąĢąĄ ąŠčéą╗ąĖčćąĖąĄ ą▓ č鹊ą╝, čćč鹊 čćąĖčüą╗ąŠ ą║ąŠąĮą▓ąĄčĆčéąĖčĆčāąĄą╝čŗčģ ą┐ąŠč鹊ą║ąŠą▓ ą▒čāą┤ąĄčé čĆą░ąĘą╗ąĖčćąĮąŠ: 4 ą┤ą╗čÅ Ethernet 40GBASE-SR4 ąĖ 10 ą┤ą╗čÅ Ethernet 100GBASE-SR10, ą░ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗąĄ ą┐ąŠč鹊ą║ąĖ ąĮąĄ ą▒čāą┤čāčé čüąŠą▒ąĖčĆą░čéčīčüčÅ/čĆą░ąĘą▒ąĖčĆą░čéčīčüčÅ ąĮą░ čüč鹊čĆąŠąĮąĄ ą┐ąĄčĆąĄą┤ą░čćąĖ/ą┐čĆąĖąĄą╝ą░ čü ą┐ąŠą╝ąŠčēčīčÄ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆąŠą▓/ą┤ąĄą╝čāą╗čīčéąĖ-ą┐ą╗ąĄą║čüąŠčĆąŠą▓ WDM, ą░ ą▒čāą┤čāčé ą┐ąĄčĆąĄą┤ą░ą▓ą░čéčīčüčÅ ąŠčéą┤ąĄą╗čīąĮąŠ.

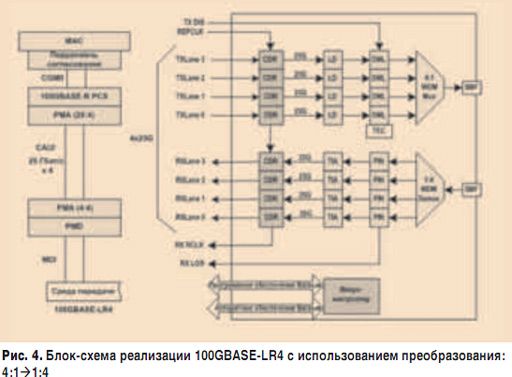

ąĀą░čüčüą╝ąŠčéčĆąĖą╝ ą▒ąŠą╗ąĄąĄ ą┐ąŠą┤čĆąŠą▒ąĮąŠ ą▓ąŠąĘą╝ąŠąČąĮčŗąĄ čüčģąĄą╝čŗ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ 100GBE čéąĖą┐ą░ 100GBASE-LR4.

ąĪąŠą│ą╗ą░čüąĮąŠ čüčéą░ąĮą┤ą░čĆčéčā [8] ąĖ čĆąĖčü. 3 čŹč鹊čé čéąĖą┐ Ethernet čĆąĄą░ą╗ąĖąĘčāąĄčéčüčÅ ą┐ąŠ 4-ą┐ąŠč鹊čć-ąĮąŠą╣ čüčģąĄą╝ąĄ čü WDM-ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖąĄą╝ 4 ąĮąĄčüčāčēąĖčģ: 1295, 1300, 1305 ąĖ 1310 ąĮą╝, ą▓čŗą▒čĆą░ąĮąĮčŗčģ ą▓ąŠ ą▓č鹊čĆąŠą╝ ąŠą║ąĮąĄ ą┐čĆąŠąĘčĆą░čćąĮąŠčüčéąĖ ą┐ąŠ čüčéą░ąĮą┤ą░čĆčéąĮąŠą╣ čüąĄčéą║ąĄ ITU-T G.694.1 čü čłą░ą│ąŠą╝ 800 ąōąōčå [7]. ą¤ąĄčĆąĄą┤ą░čćą░ ą▓ ą┤čāą┐ą╗ąĄą║čüąĮąŠą╝ čĆąĄąČąĖą╝ąĄ ąŠčüčāčēąĄčüčéą▓ą╗čÅąĄčéčüčÅ ą┐ąŠ ą┤ą▓čāą╝ ą×ąÆ.

ąĢčüą╗ąĖ ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖą╣ 100GbE, ąŠčĆąĖąĄąĮčéąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĮą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖčģ čüąĖą│ąĮą░ą╗ąŠą▓, čģą░čĆą░ą║č鹥čĆąĮąŠ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ 10-ą│ąĖą│ą░ą▒ąĖčéąĮčŗčģ ą┐ąŠč鹊ą║ąŠą▓, č鹊 ą┤ą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖą╣, ąŠčĆąĖąĄąĮčéąĖčĆąŠą▓ą░ąĮąĮčŗčģ ąĮą░ ąŠą┐čéąĖč湥čüą║ąĖąĄ čüąĖą│ąĮą░ą╗čŗ, čģą░čĆą░ą║č鹥čĆąĮąŠ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ 25-ą│ąĖą│ą░ą▒ąĖčéąĮčŗčģ ą┐ąŠč鹊ą║ąŠą▓. ąØą░ čŹčéčā čüčģąĄą╝čā ąŠčĆąĖąĄąĮčéąĖčĆąŠą▓ą░ąĮą░ ą▓ čåąĄą╗ąŠą╝ ąĖ čĆąĄą░ą╗ąĖąĘą░čåąĖčÅ 100GBASE-LR4. ąŚą┤ąĄčüčī ą╗ąŠą│ąĖčćąĮąŠ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąĖ 25-ą│ąĖą│ą░ą▒ąĖčéąĮčŗąĄ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖąĄ ą┐ąŠč鹊ą║ąĖ (ą║ą░ą║ ą┐čĆąĄą┤ą╗ąŠąČąĖą╗ ążąŠčĆčāą╝ ąŠą┐čéąĖč湥čüą║ąŠą│ąŠ čüąĄč鹥ą▓ąŠą│ąŠ ą▓ąĘą░ąĖą╝ąŠą┤ąĄą╣čüčéą▓ąĖčÅ ŌĆō OIF).

ą×ą┤ąĮą░ą║ąŠ ą┤ą╗čÅ ą╝ąŠą┤čāą╗ąĄą╣ ą┐ąĄčĆą▓ąŠą│ąŠ ą┐ąŠą║ąŠą╗ąĄąĮąĖčÅ ą▒čŗą╗ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮą░ ą░čĆčģąĖč鹥ą║čéčāčĆą░ čü 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖą╝ ąĖąĮč鹥čĆč乥ą╣čüąŠą╝ 10-ą│ąĖą│ą░ą▒ąĖčéąĮąŠą│ąŠ 10-ą┐ąŠč鹊čćąĮąŠą│ąŠ CAUI (10čģ10 ąōą▒ąĖčé/čü), čāčćąĖčéčŗą▓ą░čÅ ąĮą░ą╗ąĖčćąĖąĄ ą│ąŠč鹊ą▓čŗčģ ą╝ąŠą┤čāą╗ąĄą╣, čĆą░ąĘčĆą░ą▒ąŠčéą░ąĮąĮčŗčģ ą┤ą╗čÅ 10GE. ą×ąĮą░ čéčĆąĄą▒ąŠą▓ą░ą╗ą░ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ čüąĄčĆąĖą░-ą╗ą░ą╣ąĘąĄčĆą░ ąĮą░ ą┐ąĄčĆąĄą┤ą░čÄčēąĄą╣ čüč鹊čĆąŠąĮąĄ ą╝ąŠą┤čāą╗čÅ, ą║ąŠąĮą▓ąĄčĆčéąĖčĆčāčÄčēąĄą│ąŠ 10 ą┐ąŠč鹊ą║ąŠą▓ ą▓ 4 (10:4), ąĖ ą┤ąĄčüąĄčĆąĖą░ą╗ą░ą╣ąĘąĄčĆą░ ąĮą░ ą┐čĆąĖąĄą╝ąĮąŠą╣ čüč鹊čĆąŠąĮąĄ ą╝ąŠą┤čāą╗čÅ, ąŠčüčāčēąĄčüčéą▓ą╗čÅčÄčēąĄą│ąŠ ąŠą▒čĆą░čéąĮčāčÄ ą║ąŠąĮą▓ąĄčĆčéą░čåąĖčÄ (4:10). ąØąŠ čŹčéąĖ ą║ąŠąĮą▓ąĄčĆč鹥čĆčŗ čāą▓ąĄą╗ąĖčćąĖą▓ą░ą╗ąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą╝ąŠą┤čāą╗čÅ, čłąĖčĆąĖąĮčā ąĖąĮč鹥čĆč乥ą╣čüą░ CAUI ąĖ čĆą░ąĘą╝ąĄčĆčŗ ą╝ąŠą┤čāą╗čÅ.

ąŁč鹊ą│ąŠ ą╝ąŠąČąĮąŠ ąĖąĘą▒ąĄąČą░čéčī, ąĖčüą┐ąŠą╗čīąĘčāčÅ 25-ą│ąĖą│ą░ą▒ąĖčéąĮčŗą╣ 菹╗ąĄą║čéčĆąĖč湥čüą║ąĖą╣ ąĖąĮč鹥čĆč乥ą╣čü, ą┐čĆąĄą┤ą╗ą░ą│ą░ąĄą╝čŗą╣ OIF. ąØą░ čŹč鹊ą╝ ąĖ ąŠčüąĮąŠą▓ą░ąĮą░ ą▒ą╗ąŠą║-čüčģąĄą╝ą░ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ 100GBASE-LR4 ąĮąŠą▓ąŠą│ąŠ ą┐ąŠą║ąŠą╗ąĄąĮąĖčÅ čü ą▒ąŠą╗ąĄąĄ ą┐čĆąŠčüč鹊ą╣ čüčģąĄą╝ąŠą╣ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░ąĮąĖčÅ: 4:1?1:4, ą┐čĆąĖą▓ąĄą┤ąĄąĮąĮąŠą╣ ąĮą░ čĆąĖčü. 4. ą¤čĆąĖ ąŠčéčüčāčéčüčéą▓ąĖąĖ ą▒ą╗ąŠą║ąŠą▓ ą║ąŠąĮą▓ąĄčĆčéą░čåąĖąĖ 菹ĮąĄčĆą│ąŠą┐ąŠčéčĆąĄą▒ą╗ąĄąĮąĖąĄ ą╝ąŠą┤čāą╗čÅ čüčāčēąĄčüčéą▓ąĄąĮąĮąŠ ąĮąĖąČąĄ, ą░ ąĄą│ąŠ čĆą░ąĘą╝ąĄčĆčŗ ą┐čĆą░ą║čéąĖč湥čüą║ąĖ čüą▓ąŠą┤čÅčéčüčÅ ą║ čĆą░ąĘą╝ąĄčĆą░ą╝ ą╝ąŠą┤čāą╗čÅ 10GBE [11].

ąøąĖč鹥čĆą░čéčāčĆą░

ąĪčéą░čéčīčÅ ą┐ąŠčüčéčāą┐ąĖą╗ą░ ą▓ čĆą░ą┤ą░ą║čåąĖčÄ ąČčāčĆąĮą░ą╗ą░ ąóąĪąĪ 31.05.2011 ą│.

ą×ą┐čāą▒ą╗ąĖą║ąŠą▓ą░ąĮąŠ: ą¢čāčĆąĮą░ą╗ "ąóąĄčģąĮąŠą╗ąŠą│ąĖąĖ ąĖ čüčĆąĄą┤čüčéą▓ą░ čüą▓čÅąĘąĖ" #1, 2012

ą¤ąŠčüąĄčēąĄąĮąĖą╣: 18249

ąĪčéą░čéčīąĖ ą┐ąŠ č鹥ą╝ąĄ

ąÉą▓č鹊čĆ

| |||

ąÆ čĆčāą▒čĆąĖą║čā "ąĀąĄčłąĄąĮąĖčÅ ąŠą┐ąĄčĆą░č鹊čĆčüą║ąŠą│ąŠ ą║ą╗ą░čüčüą░" | ąÜ čüą┐ąĖčüą║čā čĆčāą▒čĆąĖą║ | ąÜ čüą┐ąĖčüą║čā ą░ą▓č鹊čĆąŠą▓ | ąÜ čüą┐ąĖčüą║čā ą┐čāą▒ą╗ąĖą║ą░čåąĖą╣